# LMH6654/LMH6655

# Single/Dual Low Power, 250 MHz, Low Noise Amplifiers

25-05689

# **General Description**

The LMH6654/LMH6655 single and dual high speed, voltage feedback amplifiers are designed to have unity-gain stable operation with a bandwidth of 250 MHz. They operate from ±2.5V to ±6V and each channel consumes only 4.5 mA. The amplifiers feature very low voltage noise and wide output swing to maximize signal-to-noise ratio.

The LMH6654/LMH6655 have a true single supply capability with input common mode voltage range extending 150 mV below negative rail and within 1.3V of the positive rail.

LMH6654/LMH6655 high speed and low power combination make these products an ideal choice for many portable, high speed application where power is at a premium.

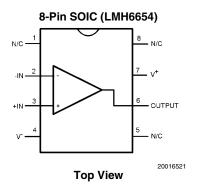

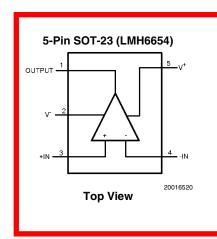

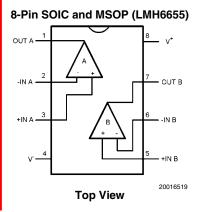

The LMH6654 is packaged in 5-Pin SOT-23 and 8-Pin SOIC. The LMH6655 is packaged in 8-Pin MSOP and 8-Pin SOIC.

The LMH6654/LMH6655 are built on National's Advance VIP10™ (Vertically Integrated PNP) complementary bipolar process.

# **Features**

$(V_S = \pm 5V, T_A = 25^{\circ}C, Typical values unless specified).$

- Voltage feedback architecture

- Unity gain bandwidth 250 MHz ±2.5V to ±6V Supply voltage range

- Slew rate 200 V/usec

- Supply current 4.5 mA/channel -5.15V to +3.7V Input common mode voltage

- Output voltage swing  $(R_1 = 100\Omega)$ -3.6V to 3.4V

- Input voltage noise 4.5 nV/√Hz

- 1.7 pA/√Hz Input current noise 25 ns

- Settling Time to 0.01%

# **Applications**

- ADC drivers

- Consumer video

- Active filters

- Pulse delay circuits

- xDSL receiver

- Pre-amps

# **Typical Performance Characteristics**

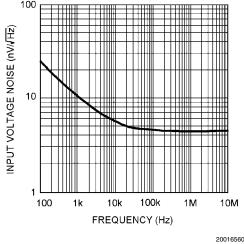

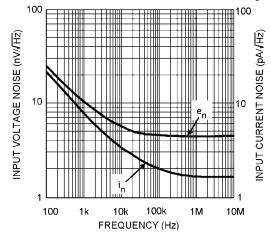

# Input Voltage Noise vs. Frequency

# 35 30

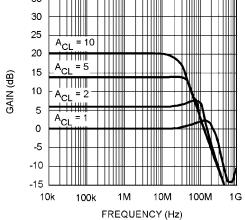

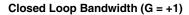

**Closed Loop Gain vs. Frequency**

20016558

VIP10™ is a trademark of National Semiconductor Corporation.

# **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

ESD Tolerance (Note 2)

Human Body Model 2 kV

Machine Model 200V  $V_{IN}$  Differential  $\pm 1.2V$ Output Short Circuit Duration (Note 3)

Supply Voltage (V+ - V-) 13.2V

Voltage at Input pins V+ +0.5V, V- -0.5V

Storage Temperature Range -65°C to +150°C

Junction Temperature (Note 4) +150°C

Soldering Information

Infrared or Convection (20 sec.) 235°C

Wave Soldering (10 sec.) 260°C

# **Operating Ratings** (Note 1)

# ±5V Electrical Characteristics

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V^+ = +5V$ ,  $V^- = -5V$ ,  $V_{CM} = 0V$ ,  $A_V = +1$ ,  $R_F = 25\Omega$  for gain = +1,  $R_F = 402\Omega$  for gain =  $\geq$  +2, and  $R_I = 100\Omega$ . **Boldface** limits apply at the temperature extremes.

| Symbol             | Parameter                     | Conditions                                   | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6) | Units  |  |

|--------------------|-------------------------------|----------------------------------------------|-----------------|-----------------|-----------------|--------|--|

| Dynamic F          | Performance                   | L                                            | (14010-0)       | (14010-0)       | (14010-0)       |        |  |

| - Julianii I       |                               | A <sub>V</sub> = +1                          |                 | 250             |                 |        |  |

|                    | Close Loop Bandwidth          | $A_V = +2$                                   |                 | 130             |                 |        |  |

| f <sub>CL</sub>    |                               | $A_V = +5$                                   |                 | 52              |                 | MHz    |  |

|                    |                               | $A_V = +10$                                  |                 | 26              |                 |        |  |

| 001110             | Gain Bandwidth Product        | A <sub>V</sub> ≥ +5                          |                 | 260             |                 | MHz    |  |

| GBWP               | Bandwidth for 0.1 dB Flatness | A <sub>V</sub> +1                            |                 | 18              |                 | MHz    |  |

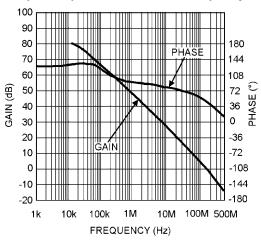

| φm                 | Phase Margin                  |                                              |                 | 50              |                 | deg    |  |

| SR                 | Slew Rate (Note 8)            | $A_V = +1, V_{IN} = 2 V_{PP}$                |                 | 200             |                 | V/µs   |  |

| t <sub>s</sub>     | Settling Time 0.01%           | A <sub>V</sub> = +1, 2V Step                 |                 | 25              |                 | ns     |  |

| Ü                  | 0.1%                          |                                              |                 | 15              |                 | ns     |  |

| t <sub>r</sub>     | Rise Time                     | A <sub>V</sub> = +1, 0.2V Step               |                 | 1.4             |                 | ns     |  |

| t <sub>f</sub>     | Fall Time                     | A <sub>V</sub> = +1, 0.2V Step               |                 | 1.2             |                 | ns     |  |

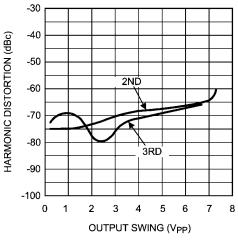

| Distortion         | and Noise Response            |                                              |                 |                 |                 |        |  |

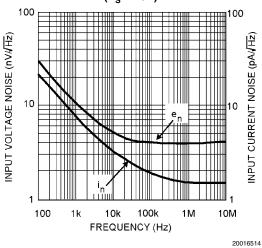

| e <sub>n</sub>     | Input Referred Voltage Noise  | f ≥ 0.1 MHz                                  |                 | 4.5             |                 | nV/√Hz |  |

| i <sub>n</sub>     | Input-Referred Current Noise  | f ≥ 0.1 MHz                                  |                 | 1.7             |                 | pA/√Hz |  |

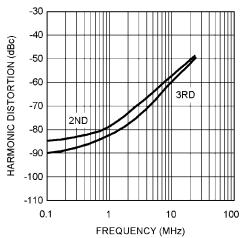

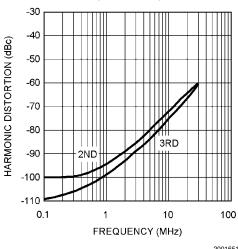

|                    | Second Harmonic Distortion    | A <sub>V</sub> = +1, f = 5 MHz               |                 | -80             |                 | JD.    |  |

|                    | Third Harmonic Distortion     | $V_{O} = 2 V_{PP}, R_{L} = 100 \Omega$       |                 | -85             |                 | dBc    |  |

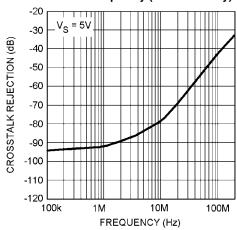

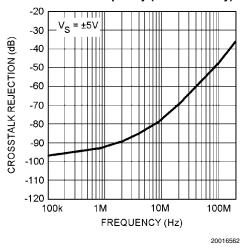

| X <sub>t</sub>     | Crosstalk (for LMH6655 only)  | Input Referred, 5 MHz,<br>Channel-to-Channel |                 | -80             |                 | dB     |  |

| DG                 | Differential Gain             | $A_V = +2$ , NTSC, $R_L = 150\Omega$         |                 | 0.01            |                 | %      |  |

| DP                 | Differential Phase            | $A_V = +2$ , NTSC, $R_L = 150\Omega$         |                 | 0.025           |                 | deg    |  |

| Input Cha          | racteristics                  | •                                            | •               | •               | •               | •      |  |

| V <sub>OS</sub>    | Input Offset Voltage          | V <sub>CM</sub> = 0V                         | -3<br><b>-4</b> | ±1              | 3<br><b>4</b>   | mV     |  |

| TC V <sub>os</sub> | Input Offset Average Drift    | V <sub>CM</sub> = 0V (Note 7)                |                 | 6               |                 | μV/°C  |  |

| I <sub>B</sub>     | Input Bias Current            | V <sub>CM</sub> = 0V                         |                 | 5               | 12<br><b>18</b> | μΑ     |  |

| I <sub>os</sub>    | Input Offset Current          | V <sub>CM</sub> = 0V                         | -1<br>-2        | 0.3             | 1<br>2          | μΑ     |  |

| В                  | Input Resistance              | Common Mode                                  |                 | 4               |                 | МΩ     |  |

| $R_{IN}$           |                               | Differential Mode                            |                 | 20              |                 | kΩ     |  |

| Symbol           | Parameter                        | Conditions                                               | Min<br>(Note 6)   | Typ<br>(Note 5) | Max<br>(Note 6)     | Units |  |

|------------------|----------------------------------|----------------------------------------------------------|-------------------|-----------------|---------------------|-------|--|

| C <sub>IN</sub>  | Input Capacitance                | Common Mode                                              |                   | 1.8             |                     |       |  |

|                  |                                  | Differential Mode                                        |                   | 1               |                     | pF    |  |

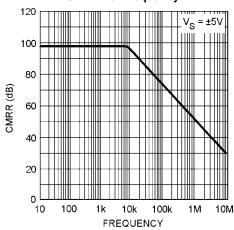

| CMRR             | Common Mode Rejection Ration     | Input Referred,<br>V <sub>CM</sub> = 0V to -5V           | 70<br><b>68</b>   | 90              |                     | dB    |  |

| CMVR             | Input Common- Mode Voltage Range | CMRR ≥ 50 dB                                             | 3.5               | -5.15<br>3.7    | -5.0                | ٧     |  |

| Transfer C       | l<br>Characteristics             |                                                          | 0.0               | 0.7             |                     |       |  |

| A <sub>VOL</sub> | Large Signal Voltage Gain        | $V_{O} = 4 V_{PP}, R_{L} = 100\Omega$                    | 60<br><b>58</b>   | 67              |                     | dB    |  |

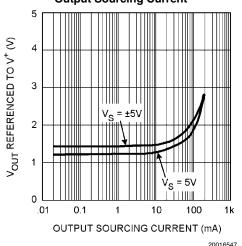

| Output Ch        | aracteristics                    | •                                                        | •                 | •               |                     |       |  |

|                  | Output Swing High                | No Load                                                  | 3.4<br><b>3.2</b> | 3.6             |                     | V     |  |

| V <sub>O</sub>   | Output Swing Low                 | No Load                                                  |                   | -3.9            | −3.7<br><b>−3.5</b> |       |  |

|                  | Output Swing High                | R <sub>L</sub> = 100Ω                                    | 3.2<br><b>3.0</b> | 3.4             |                     |       |  |

|                  | Output Swing Low                 | R <sub>L</sub> = 100Ω                                    |                   | -3.6            | −3.4<br><b>−3.2</b> |       |  |

|                  | Short Circuit Current (Note 3)   | Sourcing, $V_O = 0V$<br>$\Delta V_{IN} = 200 \text{ mV}$ | 145<br><b>130</b> | 280             |                     |       |  |

| I <sub>SC</sub>  |                                  | Sinking, $V_O = 0V$<br>$\Delta V_{IN} = 200 \text{ mV}$  | 100<br><b>80</b>  | 185             |                     | mA    |  |

|                  | Output Current                   | Sourcing, V <sub>O</sub> = +3V                           |                   | 80              |                     | - mA  |  |

| I <sub>OUT</sub> |                                  | Sinking, $V_O = -3V$                                     |                   | 120             |                     |       |  |

| R <sub>o</sub>   | Output Resistance                | A <sub>V</sub> = +1, f <100 kHz                          |                   | 0.08            |                     | Ω     |  |

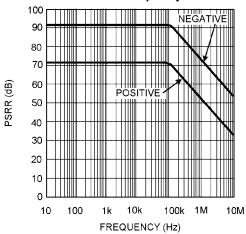

| Power Su         | pply                             | •                                                        | · ·               | •               |                     |       |  |

| PSRR             | Power Supply Rejection Ratio     | Input Referred,<br>V <sub>S</sub> = ±5V to ±6V           | 60                | 76              |                     | dB    |  |

| I <sub>S</sub>   | Supply Current (per channel)     |                                                          |                   | 4.5             | 6<br><b>7</b>       | mA    |  |

# **5V Electrical Characteristics**

Unless otherwise specified, all limits guaranteed for  $T_J = 25^{\circ}C$ ,  $V^+ = +5V$ ,  $V^- = -0V$ ,  $V_{CM} = 2.5V$ ,  $A_V = +1$ ,  $R_F = 25\Omega$  for gain = +1,  $R_F = 402\Omega$  for gain =  $\geq$  +2, and  $R_L = 100\Omega$  to V+/2. **Boldface** limits apply at the temperature extremes.

| Symbol          | Parameter                     | Conditions                     | Min<br>(Note 6) | Typ<br>(Note 5) | Max<br>(Note 6) | Units |

|-----------------|-------------------------------|--------------------------------|-----------------|-----------------|-----------------|-------|

| Dynamic I       | Performance                   | •                              |                 | •               |                 |       |

|                 | Close Loop Bandwidth          | A <sub>V</sub> = +1            |                 | 230             |                 | MHz   |

|                 |                               | A <sub>V</sub> = +2            |                 | 120             |                 |       |

| f <sub>CL</sub> |                               | A <sub>V</sub> = +5            |                 | 50              |                 |       |

|                 |                               | A <sub>V</sub> = +10           |                 | 25              |                 |       |

| GBWP            | Gain Bandwidth Product        | A <sub>V</sub> ≥ +5            |                 | 250             |                 | MHz   |

|                 | Bandwidth for 0.1 dB Flatness | A <sub>V</sub> = +1            |                 | 17              |                 | MHz   |

| φm              | Phase Margin                  |                                |                 | 48              |                 | deg   |

| SR              | Slew Rate (Note 8)            | $A_V = +1, V_{IN} = 2 V_{PP}$  |                 | 190             |                 | V/µs  |

| t <sub>S</sub>  | Settling Time 0.01%           | A <sub>V</sub> = +1, 2V Step   |                 | 30              |                 | ns    |

|                 | 0.1%                          |                                |                 | 20              |                 | ns    |

| t <sub>r</sub>  | Rise Time                     | A <sub>V</sub> = +1, 0.2V Step |                 | 1.5             |                 | ns    |

| t <sub>f</sub>  | Fall Time                     | A <sub>V</sub> = +1, 0.2V Step |                 | 1.35            |                 | ns    |

| Symbol             | Parameter                       | Conditions                                                  | Min<br>(Note 6)    | Typ<br>(Note 5) | Max<br>(Note 6)    | Units  |

|--------------------|---------------------------------|-------------------------------------------------------------|--------------------|-----------------|--------------------|--------|

| Distortion         | and Noise Response              | 1                                                           |                    | ,               | , ,                |        |

| e <sub>n</sub>     | Input Referred Voltage Noise    | f ≥ 0.1 MHz                                                 |                    | 4.5             |                    | nV/√Hz |

| n                  | Input Referred Current Noise    | f ≥ 0.1 MHz                                                 |                    | 1.7             |                    | pA√Hz  |

| ··                 | Second Harmonic Distortion      | $A_V = +1, f = 5 \text{ MHz}$                               |                    | -65             |                    |        |

|                    | Third Harmonic Distortion       | $V_0 = 2 V_{PP}, R_L = 100\Omega$                           |                    | -70             |                    | dBc    |

| X <sub>t</sub>     | Crosstalk (for LMH6655 only)    | Input Referred, 5 MHz                                       |                    | -78             |                    | dB     |

| nput Chai          | racteristics                    | •                                                           |                    |                 |                    |        |

| / <sub>os</sub>    | Input Offset Voltage            | V <sub>CM</sub> = 2.5V                                      | -5<br><b>-6.5</b>  | ±2              | 5<br><b>6.5</b>    | mV     |

| rc v <sub>os</sub> | Input Offset Average Drift      | V <sub>CM</sub> = 2.5V (Note 7)                             |                    | 6               |                    | μV/°C  |

| В                  | Input Bias Current              | V <sub>CM</sub> = 2.5V                                      |                    | 6               | 12<br><b>18</b>    | μΑ     |

| os                 | Input Offset Current            | V <sub>CM</sub> = 2.5V                                      | -2<br>-3           | 0.5             | 2<br><b>3</b>      | μΑ     |

|                    | Innut Resistance                | Common Mode                                                 |                    | 4               |                    | МΩ     |

| R <sub>IN</sub>    | Input Resistance                | Differential Mode                                           |                    | 20              |                    | kΩ     |

| ) <sub>IN</sub>    | Input Capacitance               | Common Mode                                                 |                    | 1.8             |                    | pF     |

| 7IN                |                                 | Differential Mode                                           |                    | 1               |                    |        |

| MRR                | Common Mode Rejection Ration    | Input Referred,<br>V <sub>CM</sub> = 0V to -2.5V            | 70<br><b>68</b>    | 90              |                    | dB     |

| CMVR               | Input Common Mode Voltage Range | CMRR ≥ 50 dB                                                |                    | -0.15           | 0                  | V      |

| Franciar C         | <br>Characteristics             |                                                             | 3.5                | 3.7             |                    |        |

| ransier C          | naracteristics                  | $V_{\rm O} = 1.6  V_{\rm PP},  R_{\rm I} = 100 \Omega$      | 58                 | 64              |                    |        |

| A <sub>VOL</sub>   | Large Signal Voltage Gain       | $v_0 = 1.0 v_{PP}, n_L - 10002$                             | 55                 |                 |                    | dB     |

| Output Ch          | aracteristics                   |                                                             |                    |                 |                    |        |

|                    | Output Swing High               | No Load                                                     | 3.6<br><b>3.4</b>  | 3.75            |                    |        |

| / <sub>O</sub>     | Output Swing Low                | No Load                                                     |                    | 0.9             | 1.1<br><b>1.3</b>  | V      |

|                    | Output Swing High               | R <sub>L</sub> = 100Ω                                       | 3.5<br><b>3.35</b> | 3.70            |                    |        |

|                    | Output Swing Low                | $R_L = 100\Omega$                                           |                    | 1               | 1.3<br><b>1.45</b> |        |

|                    | Short Circuit Current (Note 3)  | Sourcing , $V_0 = 2.5V$<br>$\Delta V_{IN} = 200 \text{ mV}$ | 90<br><b>80</b>    | 170             |                    | mΛ     |

| SC                 |                                 | Sinking, $V_O = 2.5V$<br>$\Delta V_{IN} = 200 \text{ mV}$   | 70<br><b>60</b>    | 140             |                    | mA     |

|                    | Output Current                  | Sourcing, V <sub>O</sub> = +3.5V                            |                    | 30              |                    | mA     |

| TUC                | Output Current                  | Sinking, V <sub>O</sub> = 1.5V                              |                    | 60              |                    |        |

| R <sub>O</sub>     | Output Resistance               | $A_V = +1$ , f <100 kHz                                     |                    | .08             |                    | Ω      |

| Power Sup          | oply                            |                                                             |                    |                 |                    |        |

| PSRR               | Power Supply Rejection Ratio    | Input Referred , $V_S = \pm 2.5V$ to $\pm 3V$               | 60                 | 75              |                    | dB     |

| S                  | Supply Current (per channel)    |                                                             |                    | 4.5             | 6<br><b>7</b>      | mA     |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications and the test conditions, see the Electrical Characteristics Table

Note 2: Human body model, 1.5 k $\Omega$  in series with 100 pF. Machine model:  $0\Omega$  in series with 100 pF.

Note 3: Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature at 150°C.

Note 4: The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$  and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_J(MAX), T_A)/(\theta_{JA})$ . All numbers apply for packages soldered directly onto a PC board.

Note 5: Typical Values represent the most likely parametric norm.

Note 6: All limits are guaranteed by testing or statistical analysis.

Note 7: Offset voltage average drift is determined by dividing the change in V<sub>OS</sub> at temperature extremes into the total temperature change.

Note 8: Slew rate is the slower of the rising and falling slew rates. Slew rate is rate of change from 10% to 90% of output voltage step.

# **Connection Diagrams**

# **Ordering Information**

| Package      | Part Number | Package Marking | Transport Media          | NSC Drawing |  |

|--------------|-------------|-----------------|--------------------------|-------------|--|

|              | LMH6654MA   | LMH6654MA       | 95 Units Rails           | M08A        |  |

| 8-Pin SOIC   | LMH6654MAX  | LIVINOOD4IVIA   | 2.5k Units Tape and Reel |             |  |

| 8-PIN 501C   | LMH6655MA   | LMUCCEEMA       | 95 Units Rails           |             |  |

|              | LMH6655MAX  | LMH6655MA       | 2.5k Units Tape and Reel |             |  |

| 5-Pin SOT-23 | LMH6654MF   | ACCA            | 1k Units Tape and Reel   | MF05A       |  |

| 5-PIN 501-23 | LMH6654MFX  | A66A            | 3K Units Tape and Reel   | IVIFUSA     |  |

| O Din MCOD   | LMH6655MM   | A C 7 A         | 1k Units Tape and Reel   | MULACOA     |  |

| 8-Pin MSOP   | LMH6655MMX  | A67A            | 3.5k Units Tape and Reel | MUA08A      |  |

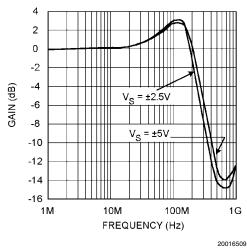

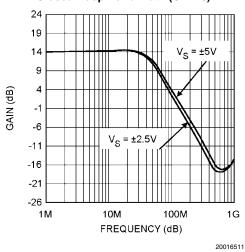

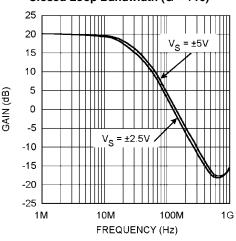

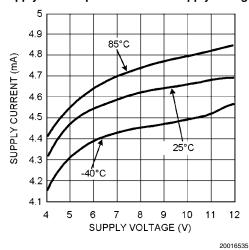

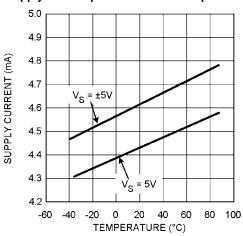

# **Typical Performance Characteristics** $T_J = 25^{\circ}\text{C}$ , $V^+ = \pm 5\text{V}$ , $V^- = -5$ , $R_F = 25\Omega$ for gain = +1, $R_F = 402\Omega$ and for gain $\geq$ +2, and $R_L = 100\Omega$ , unless otherwise specified.

# Closed Loop Bandwidth (G = +2)

20016510

# Closed Loop Bandwidth (G = +5)

# Closed Loop Bandwidth (G = +10)

20016512

# Supply Current per Channel vs. Supply Voltage

Supply Current per Channel vs. Temperature

20016548

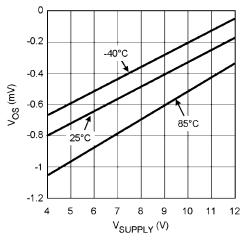

# Offset Voltage vs. Supply Voltage ( $V_{CM} = 0V$ )

20016549

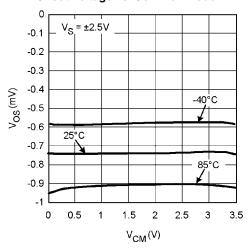

# Offset Voltage vs. Common Mode

20016539

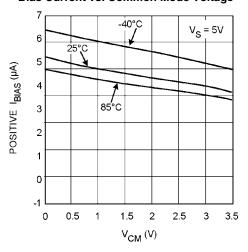

# Bias Current vs. Common Mode Voltage

20016537

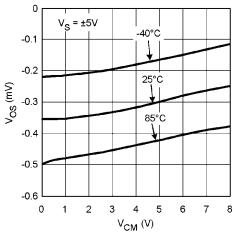

# Offset Voltage vs. Common Mode

20016532

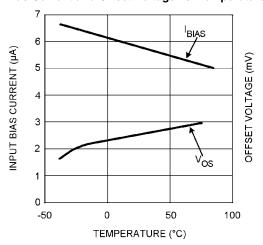

# Bias Current and Offset Voltage vs. Temperature

20016551

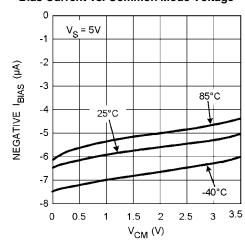

# Bias Current vs. Common Mode Voltage

20016565

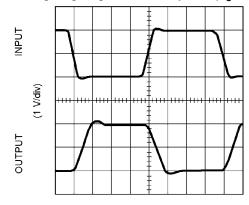

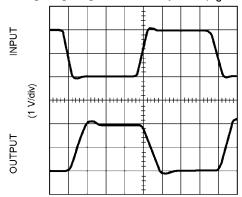

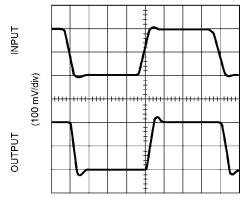

# Inverting Large Signal Pulse Response ( $V_S = 5V$ )

TIME (12.5 ns/div)

20016502

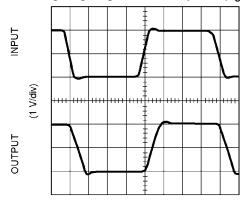

# Inverting Large Signal Pulse Response ( $V_S = \pm 5V$ )

TIME (12.5 ns/div)

20016504

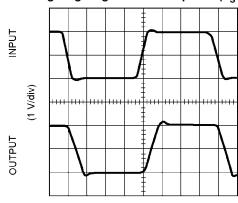

# Non-Inverting Large Signal Pulse Response ( $V_S = 5V$ )

TIME (12.5 ns/div)

20016506

# Non-Inverting Large Signal Pulse Response ( $V_S = \pm 5V$ )

TIME (12.5 ns/div)

20016508

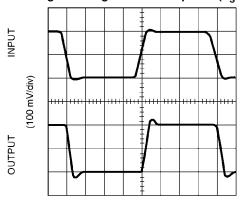

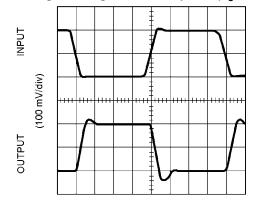

# Non-Inverting Small Signal Pulse Response ( $V_S = 5V$ )

TIME (12.5 ns/div)

20016505

# Non-Inverting Small Signal Pulse Response (V<sub>S</sub> = ±5V)

TIME (12.5 ns/div)

20016507

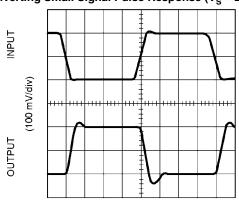

# Inverting Small Signal Pulse Response (V<sub>S</sub> = 5V)

TIME (12.5 ns/div)

20016501

# Inverting Small Signal Pulse Response ( $V_S = \pm 5V$ )

TIME (12.5 ns/div)

20016503

# Input Voltage and Current Noise vs. Frequency ( $V_S = 5V$ )

20016513

# Input Voltage and Current Noise vs. Frequency $(V_S = \pm 5V)$

Harmonic Distortion vs. Frequency G = +1,  $V_O = 2 V_{PP}$ ,  $V_S = 5 V$

20016517

# Harmonic Distortion vs. Frequency G = +1, $V_O = 2 V_{PP}$ , $V_S = \pm 5 V$

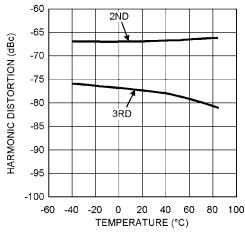

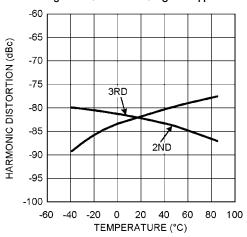

# Harmonic Distortion vs. Temperature $V_S$ = 5V, f = 5 MHz, $V_O$ = 2 $V_{PP}$

20016529

# Harmonic Distortion vs. Temperature $V_S = \pm 5V$ , f = 5 MHz, $V_O = 2$ $V_{PP}$

20016528

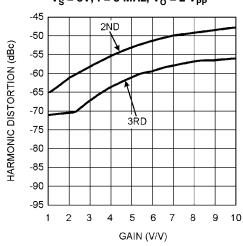

# Harmonic Distortion vs. Gain $V_S = 5V$ , f = 5 MHz, $V_O = 2$ $V_{PP}$

20016531

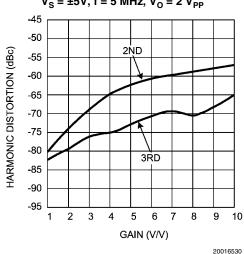

# Harmonic Distortion vs. Gain $V_S = \pm 5V$ , f = 5 MHz, $V_O = 2$ $V_{PP}$

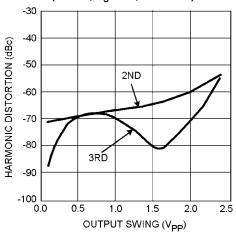

**Harmonic Distortion vs. Output Swing**  $(G = +2, V_S = 5V, f = 5 \dot{M}Hz)$

20016559

# Harmonic Distortion vs. Output Swing $(G = +2, V_S = \pm 5V, f = 5 \text{ MHz})$

20016522

# CMRR vs. Frequency

20016564

# **Output Sourcing Current**

PSRR vs. Frequency

20016516

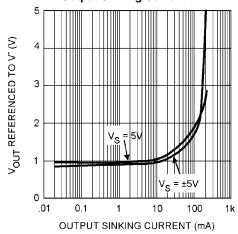

# **Output Sinking Current**

20016546

# CrossTalk vs. Frequency (LMH6655 only)

20016561

### CrossTalk vs. Frequency (LMH6655 only)

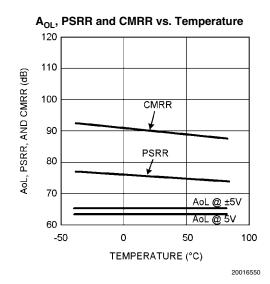

# Open Loop Gain and Phase vs. Frequency

# 20016527

# **Application Information**

# **GENERAL INFORMATION**

The LMH6654 single and LMH6655 dual high speed, voltage feedback amplifiers are manufactured on National Semiconductor's new VIP10 (Vertically Integrated PNP) complementary bipolar process. These amplifiers can operate from  $\pm 2.5 V$  to  $\pm 6 V$  power supply. They offer low supply current, wide bandwidth, very low voltage noise and large output swing. Many of the typical performance plots found in the datasheet can be reproduced if  $50\Omega$  coax and  $50\Omega$   $R_{\text{IN}}/_{\text{ROUT}}$  resistors are used.

# **CIRCUIT LAYOUT CONSIDERATION**

With all high frequency devices, board layouts with stray capacitance have a strong influence on the AC performance. The LMH6654/LMH6655 are not exception and the inverting input and output pins are particularly sensitive to the coupling of parasitic capacitance to AC ground. Parasitic capacitances on the inverting input and output nodes to ground could cause frequency response peaking and possible circuit oscillation. Therefore, the power supply, ground traces and ground plan should be placed away from the inverting input and output pins. Also, it is very important to keep the parasitic capacitance across the feedback to an absolute minimum.

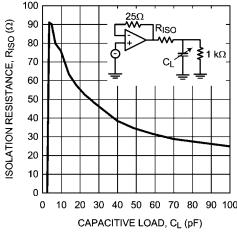

# Isolation Resistance vs. Capacitive Load

20016563

The PCB should have a ground plane covering all unused portion of the component side of the board to provide a low impedance path. All trace lengths should be minimized to reduce series inductance.

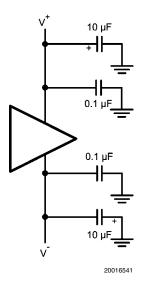

Supply bypassing is required for the amplifiers performance. The bypass capacitors provide a low impedance return current path at the supply pins. They also provide high frequency filtering on the power supply traces. It is recommended that a ceramic decoupling capacitor 0.1  $\mu F$  chip should be placed with one end connected to the ground plane and the other side as close as possible to the power pins. An additional 10  $\mu F$  tantalum electrolytic capacitor should be connected in parallel, to supply current for fast large signal changes at the output.

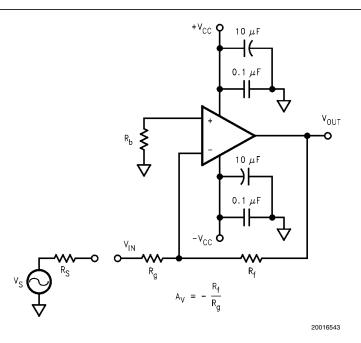

FIGURE 1.

### **EVALUATION BOARDS**

National provides the following evaluation boards as a guide for high frequency layout and as an aid in device testing and characterization.

| Device    | Package      | Evalulation<br>Board PN |

|-----------|--------------|-------------------------|

| LMH6654MF | 5-Pin SOT-23 | CLC730068               |

| LMH6654MA | 8-Pin SOIC   | CLC730027               |

| LMH6655MA | 8-Pin SOIC   | CLC730036               |

| LMH6655MM | 8-Pin MSOP   | CLC730123               |

The free evaluation board are shipped automatically when a device sample request is placed with National Semiconductor.

The CLC730027 datasheet also contains tables of recommended components to evaluate several of National's high speed amplifiers. This table for the LMH6654 is illustrated below. Refer to the evaluation board datasheet for schematics and further information.

Components Needed to Evaluate the LMH6654 on the Evaluation Board:

- R<sub>f</sub>R<sub>q</sub> use the datasheet to select values.

- R<sub>IN</sub>, R<sub>OUT</sub> typically 50Ω (Refer to the Basic Operation section of the evaluation board datasheet for details)

- R<sub>f</sub> is an optional resistor for inverting again configurations (select R<sub>f</sub> to yield desired input impedance = R<sub>n</sub>IIR<sub>f</sub>)

- C<sub>1</sub>, C<sub>2</sub> use 0.1 μF ceramic capacitors

- C<sub>3</sub>, C<sub>4</sub> use 10 μF tantalum capacitors

Components not used:

- 1. C<sub>5</sub>, C<sub>6</sub>, C<sub>7</sub>, C<sub>8</sub>

- 2. R1 thru R8

The evaluation boards are designed to accommodate dual supplies. The board can be modified to provide single operation. For best performance;

- 1) do not connect the unused supply.

- 2) ground the unused supply pin.

# **POWER DISSIPATION**

The package power dissipation should be taken into account when operating at high ambient temperature and/or high power dissipative conditions. In determining maximum operable

temperature of the device, make sure the total power dissipation of the device is considered; this power dissipated in the device with a load connected to the output as well as the nominal dissipation of the op amp.

# **DRIVING CAPACITIVE LOADS**

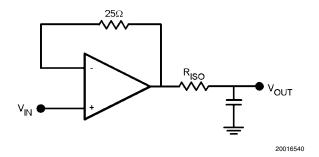

Capacitive loads decrease the phase margin of all op amps. The output impedance of a feedback amplifier becomes inductive at high frequencies, creating a resonant circuit when the load is capacitive. This can lead to overshoot, ringing and oscillation. To eliminate oscillation or reduce ringing, an isolation resistor can be placed as shown in *Figure 2* below. At frequencies above

$$F = \frac{1}{2 \pi R_{ISO} C_{IOAD}}$$

the load impedance of the Amplifier approaches  $R_{\rm ISO}.$  The desired performance depends on the value of the isolation resistor. The isolation resistance vs. capacitance load graph in the typical performance characteristics provides the means for selection of the value of  $R_S$  that provides  $\leq 3$  dB peaking in closed loop  $A_V=1$  response. In general, the bigger the isolation resistor, the more damped the pulse response becomes. For initial evaluation, a  $50\Omega$  isolation resistor is recommended.

FIGURE 2.

### COMPONENTS SELECTION AND FEEDBACK RESISTOR

It is important in high-speed applications to keep all component leads short since wires are inductive at high frequency. For discrete components, choose carbon composition axially leaded resistors and micro type capacitors. Surface mount components are preferred over discrete components for minimum inductive effect. Never use wire wound type resistors in high frequency applications.

Large values of feedback resistors can couple with parasitic capacitance and cause undesired effects such as ringing or oscillation in high-speed amplifiers. Keep resistors as low as possible consistent with output loading consideration. For a gain of 2 and higher,  $402\Omega$  feedback resistor used for the typical performance plots gives optimal performance. For unity gain follower, a  $25\Omega$  feedback resistor is recommended rather than a direct short. This effectively reduces the Q of what

would otherwise be a parasitic inductance (the feedback wire) into the parasitic capacitance at the inverting input.

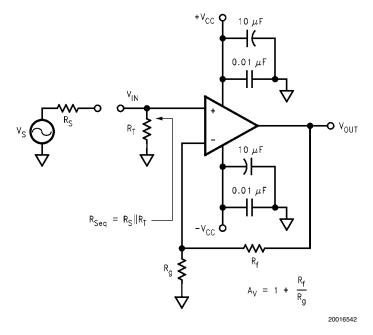

### **BIAS CURRENT CANCELLATION**

In order to cancel the bias current errors of the non-inverting configuration, the parallel combination of the gain setting  $\boldsymbol{R}_g$  and feedback  $\boldsymbol{R}_f$  resistors should equal the equivalent source resistance  $\boldsymbol{R}_{seq}$  as defined in Figure 3. Combining this constraint with the non-inverting gain equation, allows both  $\boldsymbol{R}_f$  and  $\boldsymbol{R}_g$  to be determined explicitly from the following equations:

$$R_f = A_V R_{seq}$$

and  $R_g = R_f/(A_V - 1)$

For inverting configuration, bias current cancellation is accomplished by placing a resistor  $R_b$  on the non-inverting input equal in value to the resistance seen by the inverting input  $(R_{l}/(R_g+R_s))$ . The additional noise contribution of  $R_b$  can be minimized through the use of a shunt capacitor.

FIGURE 3. Non-Inverting Amplifier Configuration

FIGURE 4. Inverting Amplifier Configuration

### **TOTAL INPUT NOISE VS. SOURCE RESISTANCE**

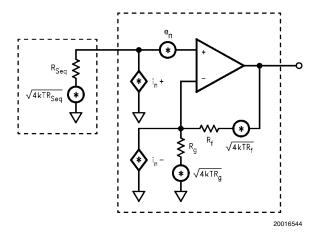

The noise model for the non-inverting amplifier configuration showing all noise sources is described in Figure 5. In addition to the intrinsic input voltage noise  $(e_n)$  and current noise  $(i_n=i_{n+}=i_{n-})$  sources, there also exits thermal voltage noise  $e_{\tau}=\sqrt{4kTR}$  associated with each of the external resistors. Equation 1 provides the general form for total equivalent input voltage noise density  $(e_{ni})$ . Equation 2 is a simplification of Equation 1 that assumes

FIGURE 5. Non-Inverting Amplifier Noise Model

$$e_{ni} = \sqrt{e_n^2 + (i_n + R_{seq})^2 + 4kTR_{seq} + (i_n - (R_f || R_g))^2 + 4kT(R_f || R_g)}$$

(1)

### **Noise Figure**

Noise Figure (NF) is a measure of the noise degradation caused by an amplifier.

NF = 10LOG

$$\left[\frac{S_i/N_i}{S_o/N_o}\right]$$

= 10LOG  $\left[\frac{e_{ni}^2}{e_t^2}\right]$  (3)

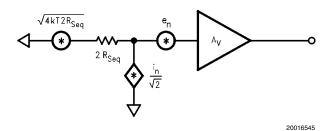

$R_f||R_g=R_{seq}$  for bias current cancellation. Figure 6 illustrates the equivalent noise model using this assumption. The total equivalent output voltage noise ( $e_{no}$ ) is  $e_{ni} * A_V$ .

FIGURE 6. Noise Model with  $R_f ||R_q = R_{seq}$

$$e_{ni} = \sqrt{e_n^2 + 2 (i_n R_{seq})^2 + 4kT (2R_{seq})}$$

(2)

If bias current cancellation is not a requirement, then  $R_f \| R_g$  does not need to equal  $R_{seq}$ . In this case, according to Equation 1,  $R_f R_g$  should be as low as possible in order to minimize noise. Results similar to Equation 1 are obtained for the inverting configuration on  $Figure\ 2$  if  $R_{seq}$  is replaced by  $R_b$  and  $R_g$  is replaced by  $R_g+R_s$ . With these substitutions, Equation 1 will yield an  $e_{ni}$  referred to the non-inverting input. Referring to  $e_{ni}$  to the inverting input is easily accomplished by multiplying  $e_{ni}$  by the ration of non-inverting to inverting gains.

The noise figure formula is shown is Equation 3. The addition of a terminating resistor  $R_{\mathsf{T}}$ , reduces the external thermal noise but increases the resulting NF.

The NF is increased because the  $\rm R_T$  reduces the input signal amplitude thus reducing the input SNR.

NF = 10 LOG

$$\left[ \frac{e_n^2 + i_n^2 (R_{seq} + (R_f || R_g)^2 + 4KTR_{seq} + 4kt (R_f || R_g)}{4kTR_{seq}} \right]$$

(4)

The noise figure is related to the equivalent source resistance  $(R_{seq})$  and the parallel combination of  $R_f$  and  $R_g$ . To minimize noise figure, the following steps are recommended:

${\sf R}_{\sf OPT}$  is the point at which the NF curve reaches a minimum and is approximated by:

$$R_{OPT} \approx (e_n/i_n)$$

- 1. Minimize  $R_f ||R_g|$

- 2. Choose the Optimum  $R_s$  ( $R_{OPT}$ )

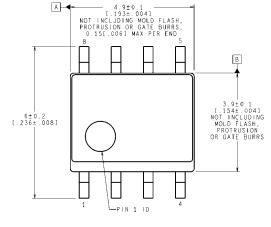

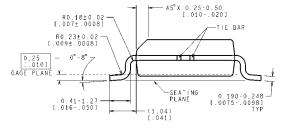

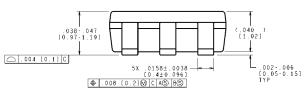

# Physical Dimensions inches (millimeters) unless otherwise noted

RECOMMENDED BAND INTERNA

CONTROLLING DIMENSION IS MILLIMETER VALUES IN [ ] ARE INCHES

DIMENSIONS IN ( ) FOR REFERENCE ONLY

M08A (Rev M)

8-Pin SOIC NS Package Number M08A

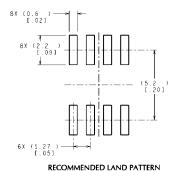

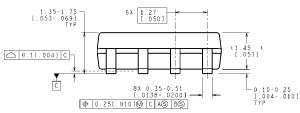

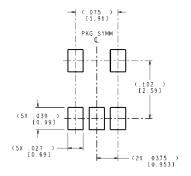

LAND PATTERN RECOMMENDATION

CONTROLLING DIMENSION IS INCH

VALUES IN [ ] ARE MILLIMETERS

DIMENSIONS IN ( ) FOR REFERENCE ONLY

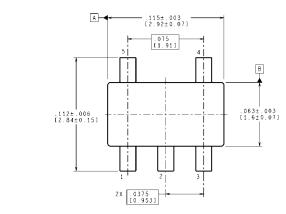

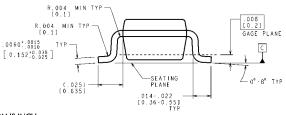

MF05A (Rev D)

5-Pin SOT-23 NS Package Number MF05A

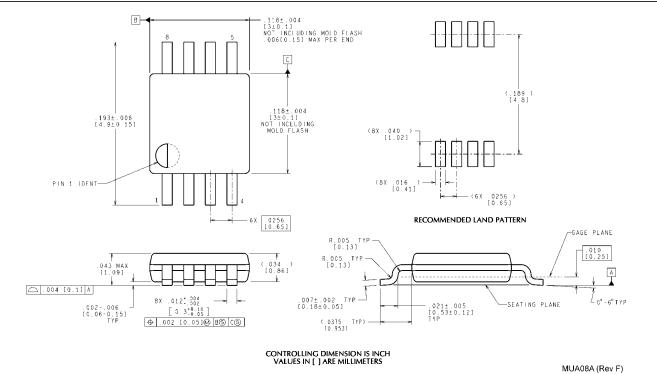

8-Pin MSOP NS Package Number MUA08A

# **Notes**

# **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pro                            | oducts                       | Design Support                  |                                |  |

|--------------------------------|------------------------------|---------------------------------|--------------------------------|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH® Tools                  | www.national.com/webench       |  |

| Audio                          | www.national.com/audio       | App Notes                       | www.national.com/appnotes      |  |

| Clock and Timing               | www.national.com/timing      | Reference Designs               | www.national.com/refdesigns    |  |

| Data Converters                | www.national.com/adc         | Samples                         | www.national.com/samples       |  |

| Interface                      | www.national.com/interface   | Eval Boards                     | www.national.com/evalboards    |  |

| LVDS                           | www.national.com/lvds        | Packaging                       | www.national.com/packaging     |  |

| Power Management               | www.national.com/power       | Green Compliance                | www.national.com/quality/green |  |

| Switching Regulators           | www.national.com/switchers   | Distributors                    | www.national.com/contacts      |  |

| LDOs                           | www.national.com/ldo         | Quality and Reliability         | www.national.com/quality       |  |

| LED Lighting                   | www.national.com/led         | Feedback/Support                | www.national.com/feedback      |  |

| Voltage Reference              | www.national.com/vref        | Design Made Easy                | www.national.com/easy          |  |

| PowerWise® Solutions           | www.national.com/powerwise   | Solutions                       | www.national.com/solutions     |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         | Mil/Aero                        | www.national.com/milaero       |  |

| Temperature Sensors            | www.national.com/tempsensors | SolarMagic™                     | www.national.com/solarmagic    |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    | PowerWise® Design<br>University | www.national.com/training      |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2009 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com